Research

Groups

Groups

MVPs

Publications

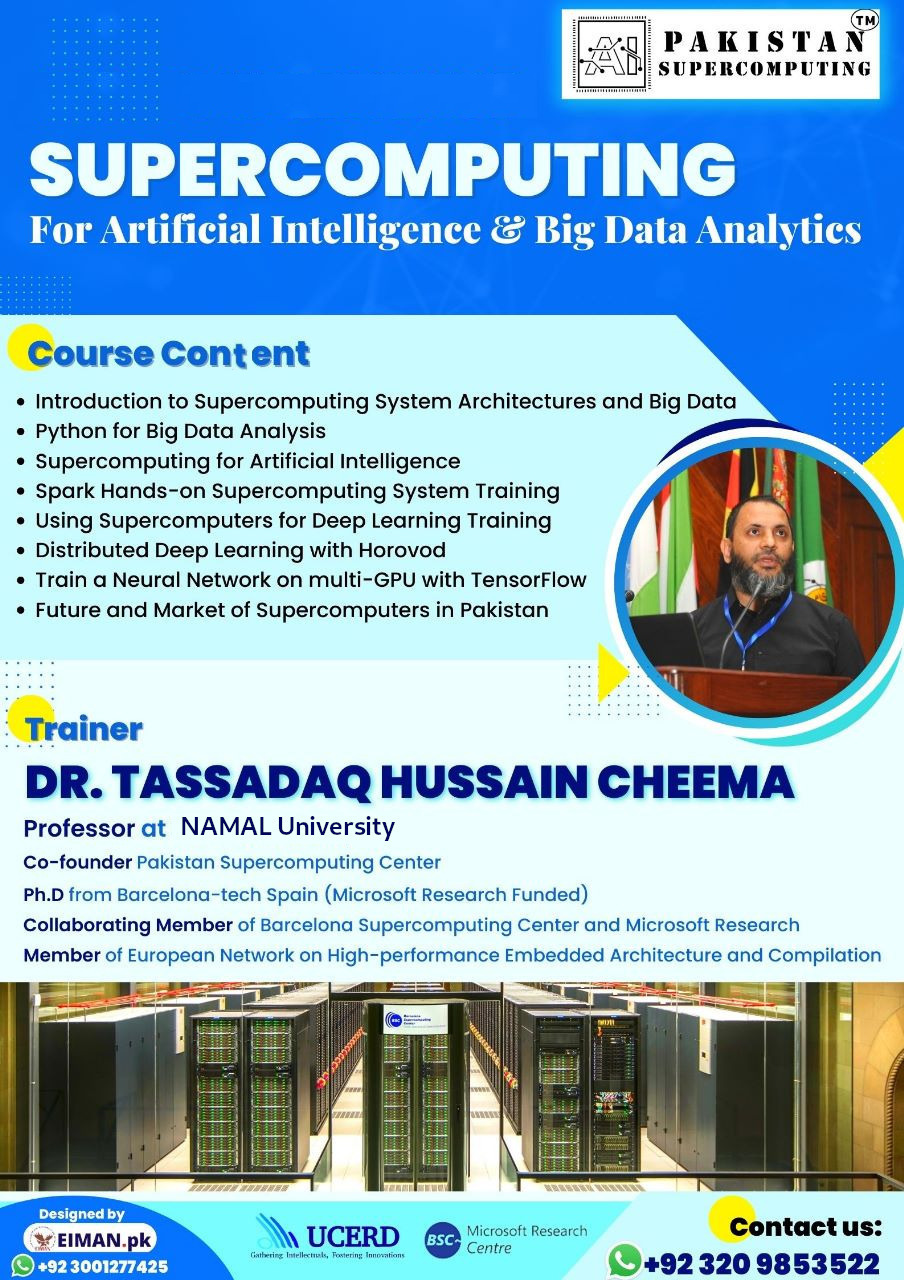

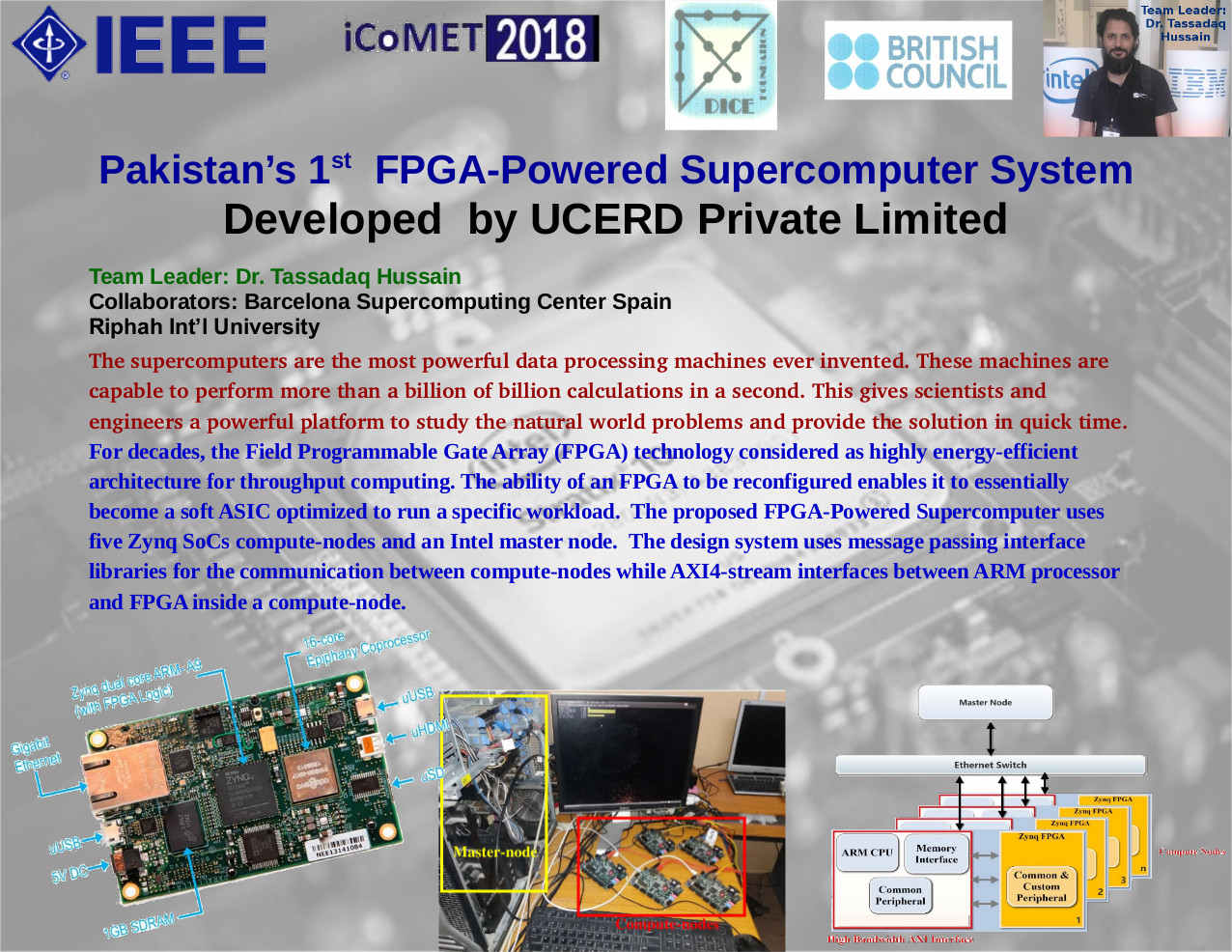

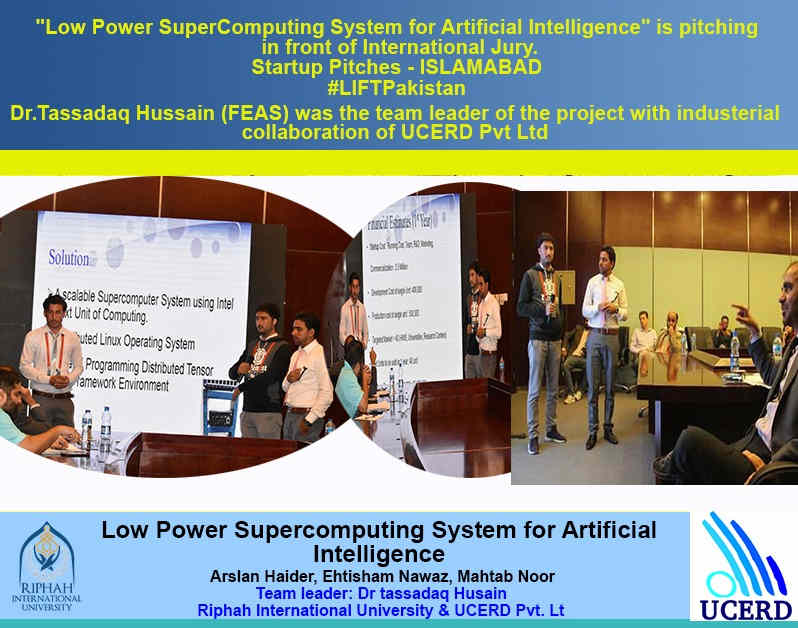

1. Supercomputing Reserch Group (ScRG)

2. Software Defined Radio Reserch Group (SDRRG)

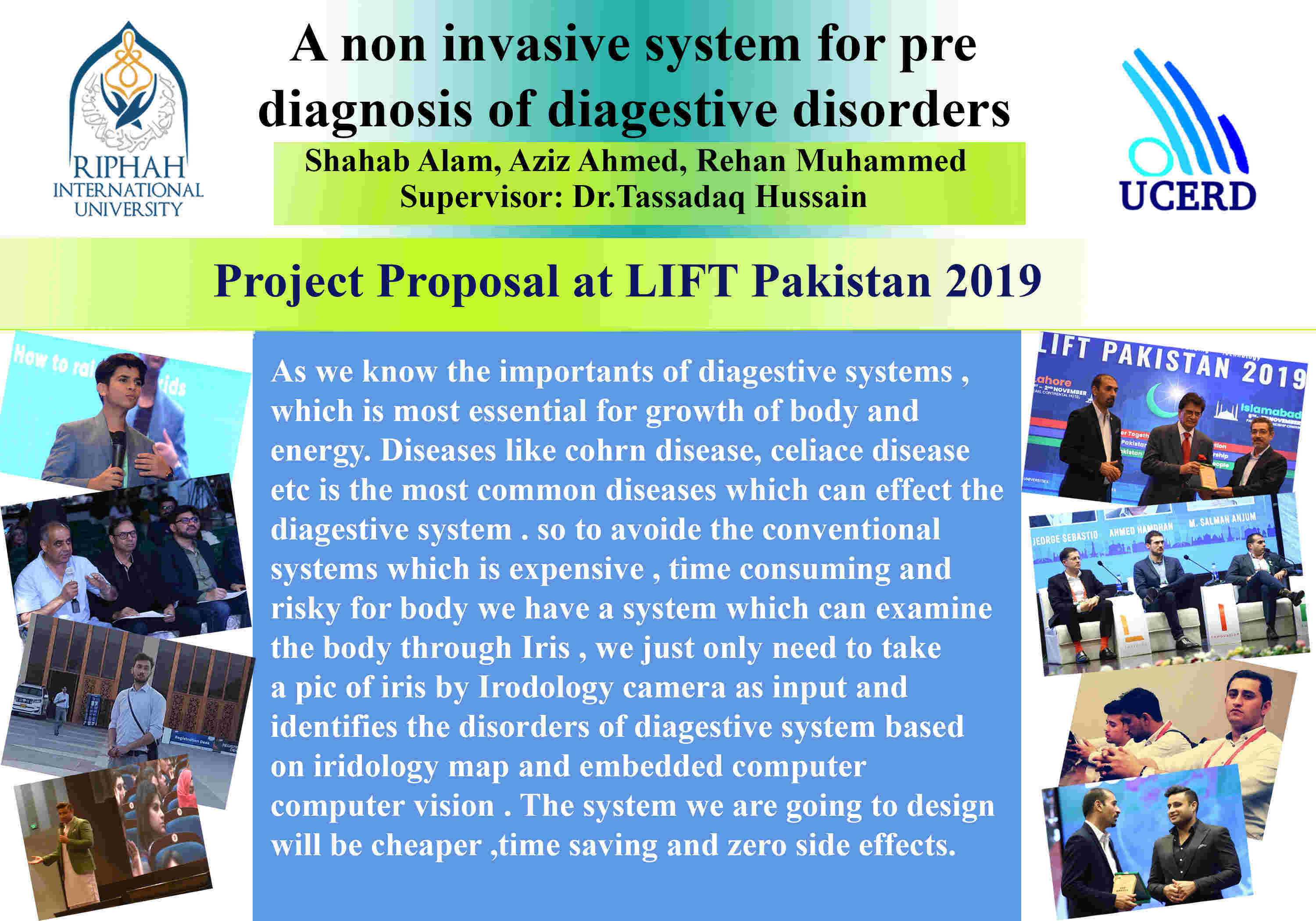

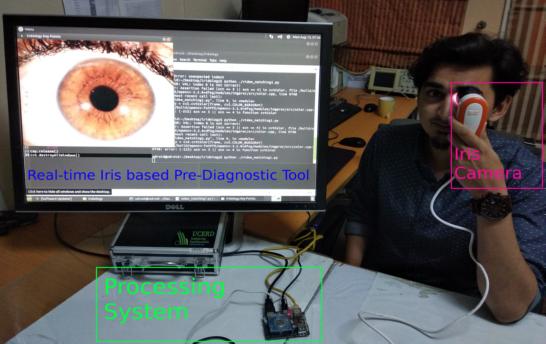

3. Iridology Research Group (IRG)

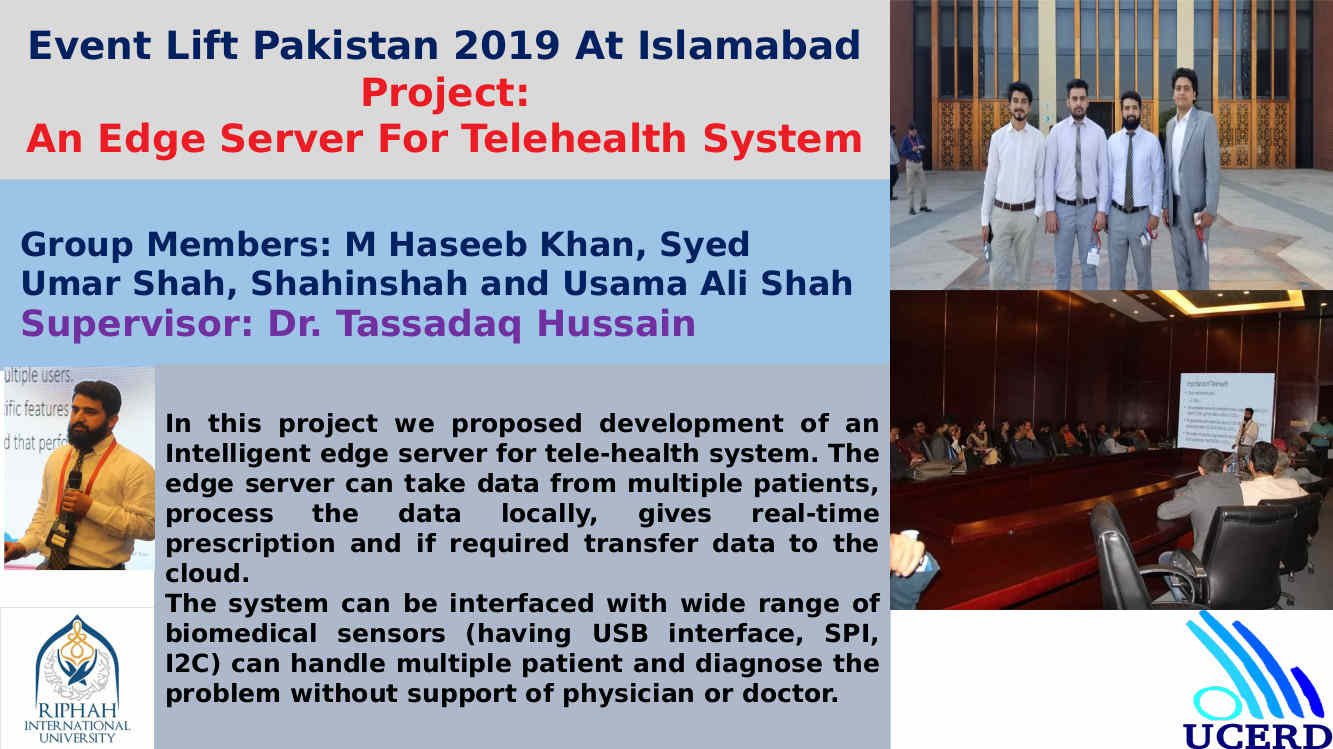

4. Medical Signal Processing Reserch Group (MSPRG)

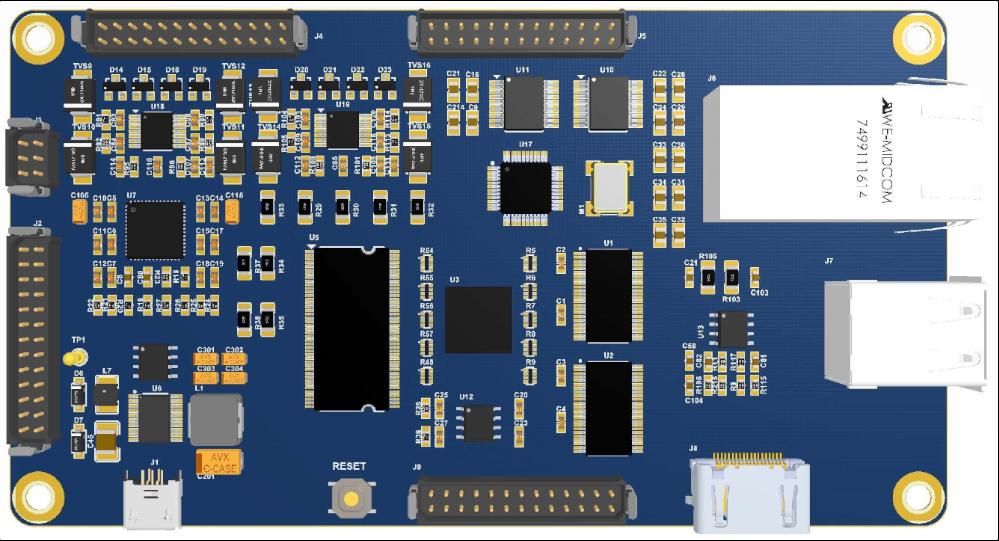

5. Digital System Design Reserch Group (DSDRG)

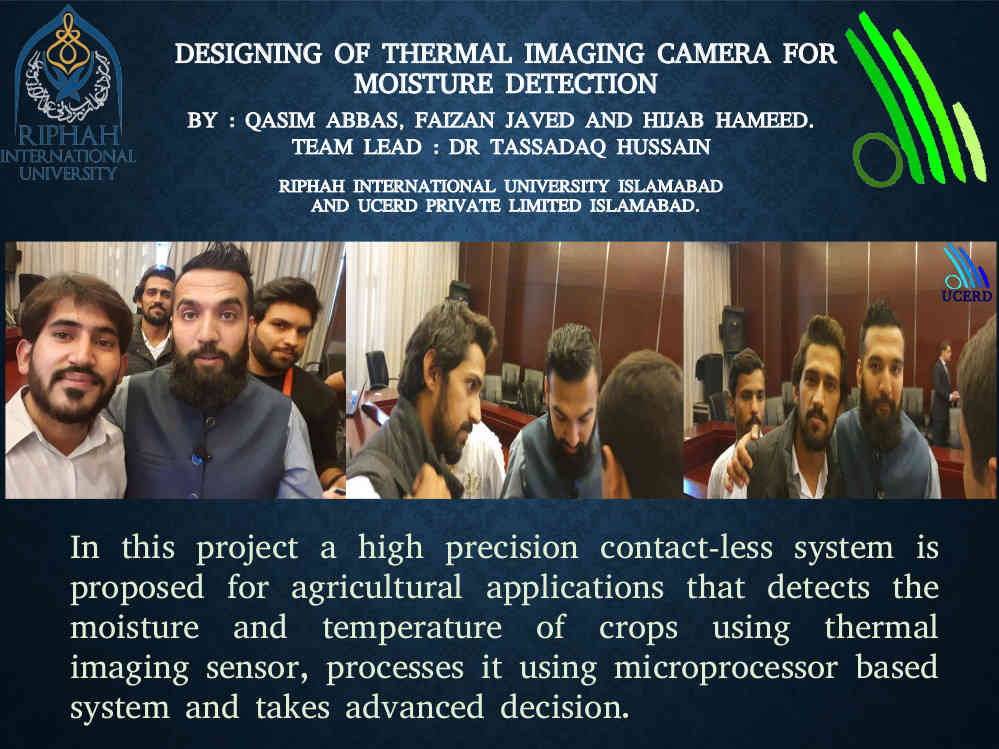

6. Data Acquisition Reserch Group (DARG)

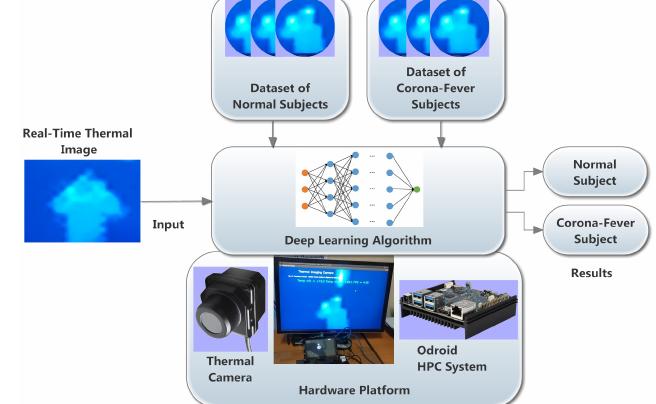

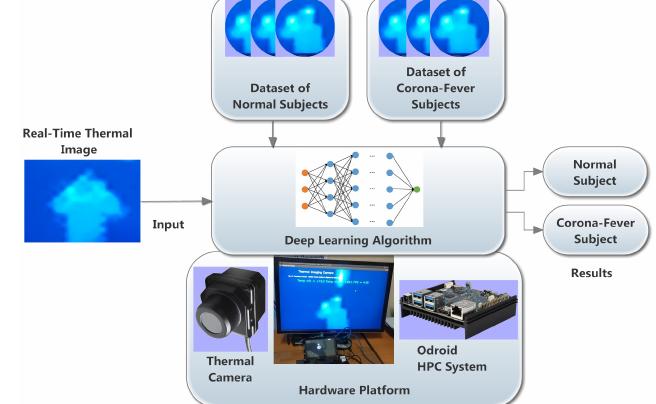

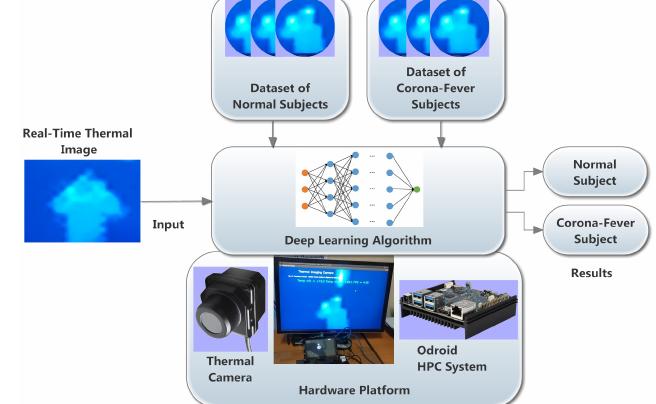

7. Embedded Computer Vision Reserch Group (ECVRG)

8. Processor based System Research Group (PSRG)

2. Software Defined Radio Reserch Group (SDRRG)

3. Iridology Research Group (IRG)

4. Medical Signal Processing Reserch Group (MSPRG)

5. Digital System Design Reserch Group (DSDRG)

6. Data Acquisition Reserch Group (DARG)

7. Embedded Computer Vision Reserch Group (ECVRG)

8. Processor based System Research Group (PSRG)

UCERD Research Groups

Get engaged with UCERD & solve a problem :

If you have passion & motivation for studies, research or development, and have an idea or instructional approach that you would present or show at the international workshop, conference or symposium, fill out below form. After few working days UCERD team will come to you with a solution for any of your studies, research or development related problem. (see example) (discussion)

Share Knowledge, Ideas and Projects Together.

Encourage, advice and guide each other.

If you have passion & motivation for studies, research or development, and have an idea or instructional approach that you would present or show at the international workshop, conference or symposium, fill out below form. After few working days UCERD team will come to you with a solution for any of your studies, research or development related problem. (see example) (discussion)

Share Knowledge, Ideas and Projects Together.

Encourage, advice and guide each other.

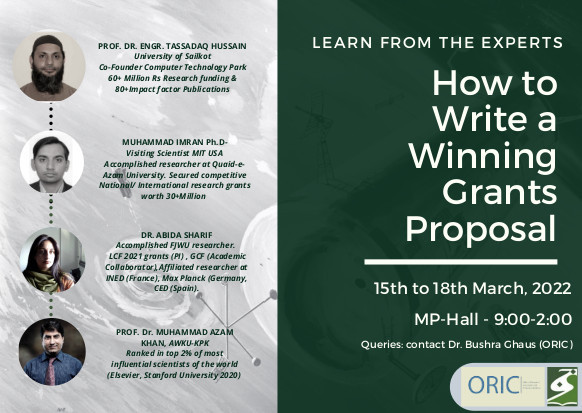

Updates and Achievements

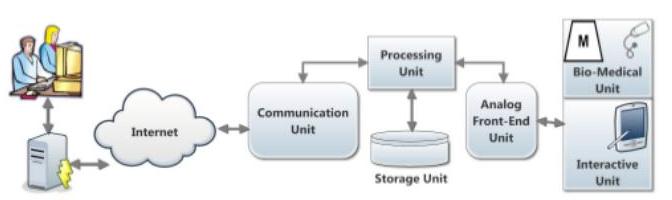

UCERD (Pvt) Ltd. is an Education Research and Development company; that gives ideas, solutions, skilled-based training, and entrepreneurship support for sustainable economic growth and industrial challenges.

UCERD plans to help science and technology by giving solutions to biological and nonbiological problems, designing and developing state-of-the-art digital systems, and engaging renowned researchers and scientists on one platform. It also gives informatics talks, and presentations and conducts workshops on different challenges and issues.

The mission of UCERD is to solve the technological problems of this age by studying, investigating, designing, and producing innovative ideas.

The ideas and solutions are based on low-power, low-cost, and high performance electronic system products for academia, industrial organizations. With this aim, special dedication has been given to fields such as Computer Sciences, Life Sciences, Earth Sciences, and Medical Applications in Science and Engineering.

UCERD religiously focuses on following the product development cycle bridging the gap between educational and industrial organizations.

UCERD plans to help science and technology by giving solutions to biological and nonbiological problems, designing and developing state-of-the-art digital systems, and engaging renowned researchers and scientists on one platform. It also gives informatics talks, and presentations and conducts workshops on different challenges and issues.

The mission of UCERD is to solve the technological problems of this age by studying, investigating, designing, and producing innovative ideas.

The ideas and solutions are based on low-power, low-cost, and high performance electronic system products for academia, industrial organizations. With this aim, special dedication has been given to fields such as Computer Sciences, Life Sciences, Earth Sciences, and Medical Applications in Science and Engineering.

UCERD religiously focuses on following the product development cycle bridging the gap between educational and industrial organizations.

UCERD Recent Developments and Products

UCERD Rawalpindi

Supercomputing Center

UCERD Murree